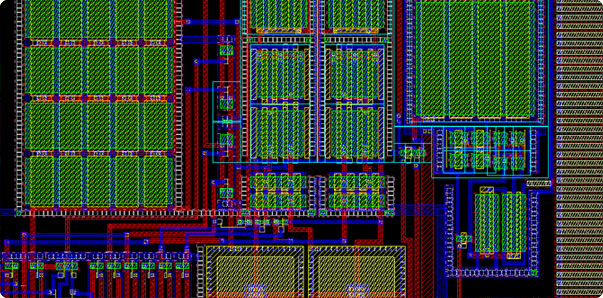

Today, the major low power design techniques used in ICs include:ĭynamic voltage scaling: The voltage of logic levels can be scaled up or down as needed to control power consumption. Initially, scaling provided the benefit of lower power consumption and higher feature density, but eventually, clock scaling increased power density to the point where new techniques were needed. Several techniques have been implemented over the past 30+ years to solve these problems. Beyond simple architectural scaling, some on-chip hardware methodologies are used to bring down power consumption. Newer technologies will need to make use of similarly innovative transistor architectures and new materials to enable further scaling. A major advance was the use of FinFETs with high-k dielectrics to ensure more complete modulation into the ON state during switching and reduced leakage current with a single solution. Reducing power in the above areas targets static and dynamic power consumption, but this has involved modifying the structure of transistors and interconnects as they have scaled over time. Sources of power dissipation and waste in VLSI The graphic below shows some of the areas and modes of operation in an IC where power consumption occurs, both during operation and in sleep/standby modes. CMOS chip architectures have lower leakage currents than much older bipolar designs, but scaling created challenges to keeping leakage current low. Even when transistors are OFF, some current leaks through gates, which is dissipated as heat. Static power consumption: This is the product of operating voltage and leakage current.CMOS logic circuits only consume power during switching, so reducing the number of switching events and ON-state voltage will reduce the total power consumption in a device. More specifically, this is the total power consumed while charging and discharging capacitances in transistor structures when logic circuits switch states. Dynamic power consumption: This is the amount of power consumed during operation.Low power design techniques in VLSI design generally fall into optimizing power consumption in four areas: The goals in implementing low power design techniques center around increasing battery life (for mobile devices), decreasing heat generation (for all other devices), or both (for smartphones and other mobile devices). Newer chip architectures used in many advanced ICs, such as SoCs for specific applications and general-purpose processors, involve packing more features on-die, which requires hardware-driven power management features to be added. Low power design techniques and new technologies balance this increase in total power consumption to ensure new products are reliable and scalable to smaller technology nodes. As more features are added to powerful processors for data center, AI, vision, and many other applications, one would expect power density in VLSI designs to increase.

Moore’s Law isn’t just a story of smaller gate sizes in transistors, it’s also a story of lower power architectures.Īs electronics continue to become miniaturized, chip designers will need to consider new ways to implement and expand on low power design techniques. Newer chips are packing as many features as possible into smaller areas with advanced processing nodes, and unique architectures are implemented to enable power-efficient signaling across the chip.

Today’s integrated circuits (ICs) are nothing like their predecessors from over two decades ago.

The trend in designing for decreased power consumption in advanced packages is not over, and newer technologies can help decrease component power consumption without sacrificing computing power.Įven after implementing low power design techniques, this GPU will dissipate a significant amount of heat Miniaturization has helped decrease power consumption in individual transistors, but it has also increased power density. Very large scale integration (VLSI) is the dominant integrated circuit (IC) design paradigm.

0 kommentar(er)

0 kommentar(er)